рефераты конспекты курсовые дипломные лекции шпоры

- Раздел Компьютеры

- /

- Справочник по командам и архитектуре Pentium

Реферат Курсовая Конспект

Справочник по командам и архитектуре Pentium

Справочник по командам и архитектуре Pentium - раздел Компьютеры, Справочник По Командам И Архитектуре Pentium....

Справочник по командам и архитектуре Pentium.

В литературе при описании команд микропроцессоров часто встречаются досадные ошибки. Стараясь избежать таких ошибок, автор выверял описание команд по нескольким источникам [3,5,6,8,9,10]. Часть команд была проверена программным путем.

Список регистров микропроцессора Pentium

Регистры общего назначения EAX = (16+AX=(AH+AL)) EBX = (16+BX=(BH+BL))Регистр CR4

0-й бит, разрешение использования виртуального флага прерываний в режиме V8086 (VME). 1-й бит, разрешение использования виртуального флага прерываний в защищенном… 2-й бит, превращение инструкции RDTSC в привилегированную (TSD).Регистры отладки

DR0…DR3 – хранят 32-битные линейные адреса точек останова. DR6 (равносильно DR4) – отражает состояние контрольных точек.Команды обмена с управляющими регистрами

Команды идентификации и управления архитектурой CPUID …Команды управления кэшированием

Команды арифметического сопроцессора.Описание работы арифметического… 1. Арифметический сопроцессор работает со своим набором команд и своим набором регистров. Однако выборку команд…Команды передачи данных

Команды сравнения данных

Арифметические команды

Трансцендентные функции

Команды управления сопроцессором

Расширение MMX использует новые типы упакованных данных: упакованные байты (восемь байт), упакованные слова (четыре слова), упакованные двойные… Команды MMX расширения(по книге [3]) EMMS Очистка стека регистров. Установка всех единиц в слове…Приложение 3. Защищенный режим микропроцессора Pentium

В главе 3.6 мы уже говорили о схеме преобразования логического адреса в физический адрес. Здесь мы дадим информацию о некоторых структурах, используемых в защищенном режиме.

В отличие от реального режима, сегментные регистры содержат в защищенном режиме не адреса, а селекторы. Рассмотрим структуру селектора.

0-1–й биты, запрошенный программой уровень привилегий.

2-й бит, определяет, использовать глобальную таблицу дескрипторов GDT (0) или локальную таблицу дескрипторов LDT (1).

3-16–й биты, индекс дескриптора в таблице.

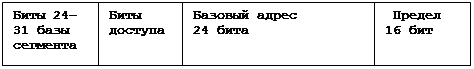

Дескриптор для защищенного режима - это 64-битная структура, которая может описывать сегмент кода, сегмент данных, сегмент состояния задачи, шлюз вызова, ловушки, прерывания или задачи. Дескриптор в глобальной дескрипторной таблице может описывать локальную дескрипторную таблицу.

Дескриптор кода и данных

Базовый адрес сегмента содержит физический адрес сегмента.

Предел содержит размер сегмента в байтах, уменьшенный на единицу.

Описание других битов.

6-й байт. Биты 0-3 определяют биты 16-19 предела. Бит 4 зарезервирован для операционной системы. Бит 5 равен 0. Бит 6 – разрядность, 0 – 16-битный, 1 – 32-битный. Бит 7 – гранулярность, 0 – лимит в байтах, 1 – лимит в 4-килобайтных величинах.

5-й байт. Бит – 0, если 1, то к сегменту было обращение. Бит 1 – разрешение чтения для кода, записи для данных. Бит 2 - бит подчиненности для кода, бит расширения для данных. Бит 3 - тип сегмента (0 – данные, 1 – код). Бит 4 - тип дескриптора (1 – не системный). Биты 5-6 – уровень привилегий дескриптора. Бит 7 - бит присутствия сегмента.

Другие дескрипторы

Если в дескрипторе бит 4 (байт 5) равен 0, то дескриптор называется системным. В этом случае биты 0-3 определяют один из возможных типов дескрипторов.

0 – зарезервированный тип.

1 – свободный 16-битный TSS (TSS – сегмент состояния задачи).

2 – дескриптор таблицы LDT.

3 – занятый 16-битный TSS.

4 – 16-битный шлюз вызова.

5 – шлюз задачи.

6 – 16-битный шлюз прерывания.

7 – 16-битный шлюз ловушки.

8 – зарезервировано.

9 – свободный 32-битный TSS.

10 – зарезервировано.

11 – занятый 32-битный TSS.

12 – 32-битный шлюз вызова.

13 – зарезервировано.

14 – 32-битный шлюз прерывания.

15 – 32-битный шлюз ловушки.

Команды CALL или JMP на адрес с селектором, указывающим на дескриптор шлюза, приводит к передаче управления по адресу, указанному в дескрипторе. Если селектор указывает на шлюз задачи, то это приводит к переключению задач. Обычные же переходы JMP, CALL, RET, IRET возможны лишь к сегментам с тем же уровнем привилегий, либо более низким уровнем привилегий.

Переключение задач

Состояние каждой задачи (значение всех регистров, связанных с данной задачей) хранится в сегменте состояния задачи (TSS), на который указывает адрес в регистре задачи. При переключении задач достаточно загрузить новый селектор в регистр задачи, и состояние старой задачи автоматически сохранится в TSS, в процессор же загрузится состояние новой задачи.

Четырехуровневая система привилегий

Уровни привилегий нумеруются от 0 до 3. Номер 3 является самым низким уровнем привилегий. Нулевой привилегией обладает ядро операционной системы. Уровни привилегий относятся к дескрипторам, селекторам и задачам. В регистре флагов имеется поле привилегий ввода-вывода, которое регулирует управление доступом к инструкциям ввода-вывода. Уровень привилегий задачи определяется двумя младшими битами сегмента CS.

При страничной адресации имеется всего два уровня доступа – 3 и 0.

Страничное управление памятью

Механизм со страничным управлением памятью включается установкой бита PG в регистре CR0. Регистр CR2 хранит линейный адрес отказа и адрес памяти, по которому был обнаружен последний отказ страницы. Регистр CR3 хранит физический адрес каталога страниц. Младшие 12 бит этого регистра всегда равны нулю (выравнивание по границе страниц). Каталог страниц состоит из 32-битных элементов и имеет длину 4 Кб.

| 20 старших бит адреса таблицы следующего уровня. | Резерв 3 бита. | G | P S | D | A | P C D | P W T | U / S | R / W | P |

Каждая таблица страниц также имеет размер 4 Кб и элементы аналогичного формата. Но эти элементы содержат базовый адрес самих страниц и атрибуты страниц. Физический адрес собирается из базового адреса и младших 12 бит линейного адреса. Значение атрибутов страниц:

G – глобальная страница, страница не удаляется из буфера.

PS – размер страницы. Если 1, то размер страницы 2 или Mb.

D – грязная страница. Устанавливается в 1 при записи на страницу.

A – бит доступа. Устанавливается в 1 при любом обращении к странице.

PCD – бит запрещения кэширования.

PWT – бит разрешения сквозной записи.

U/S – страница или таблица доступна для программ с уровнем доступа 3.

R/W – страница/таблица доступна для записи.

P – страница/таблица присутствуют.

[1] Напоминаю, что ASCII-число предполагает одну цифру на один байт, BCD-число – одну цифру на половину байта. Т.о. скажем в регистре AX, может находиться двухразрядное ASCII-число и четырехразрядное BCD-число.

[2] Мы пользуемся несколько устаревшим названием. Правильнее было бы это назвать числовым процессором.

[DS1]Явно здесь что-то не так

– Конец работы –

Используемые теги: Справочник, командам, архитектуре, Pentium0.066

Если Вам нужно дополнительный материал на эту тему, или Вы не нашли то, что искали, рекомендуем воспользоваться поиском по нашей базе работ: Справочник по командам и архитектуре Pentium

Что будем делать с полученным материалом:

Если этот материал оказался полезным для Вас, Вы можете сохранить его на свою страничку в социальных сетях:

| Твитнуть |

Хотите получать на электронную почту самые свежие новости?

Новости и инфо для студентов